必考!!

BJT、MOS

HBT优势

BiMos

自对准

第一部分

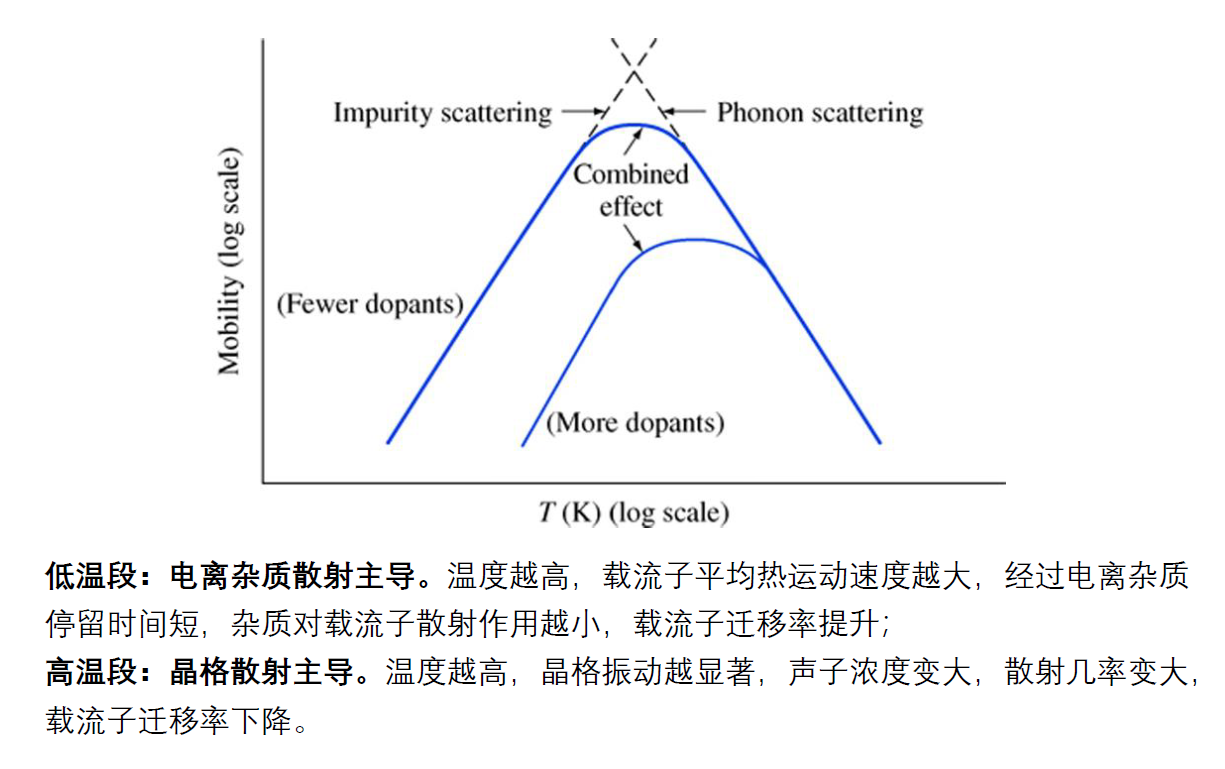

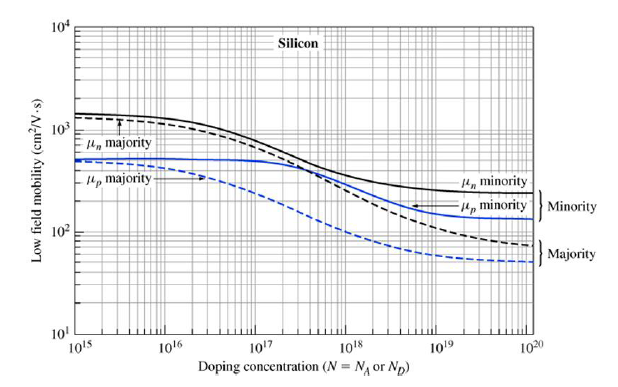

提高载流子迁移率的方法。

适当的温度

低掺杂浓度

电子显微镜的分辨率约为0.1nm,估算能达到这样的分辨率对电子需施加多大的加速电压。

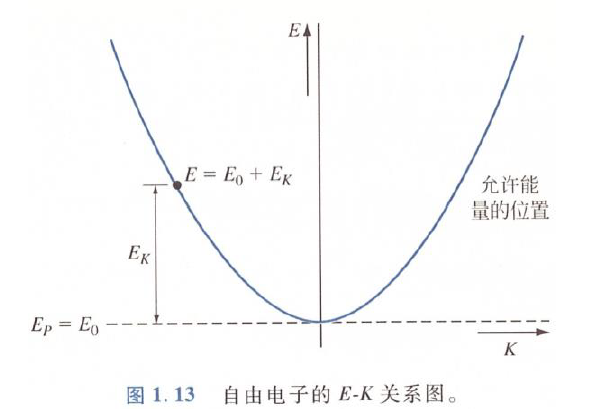

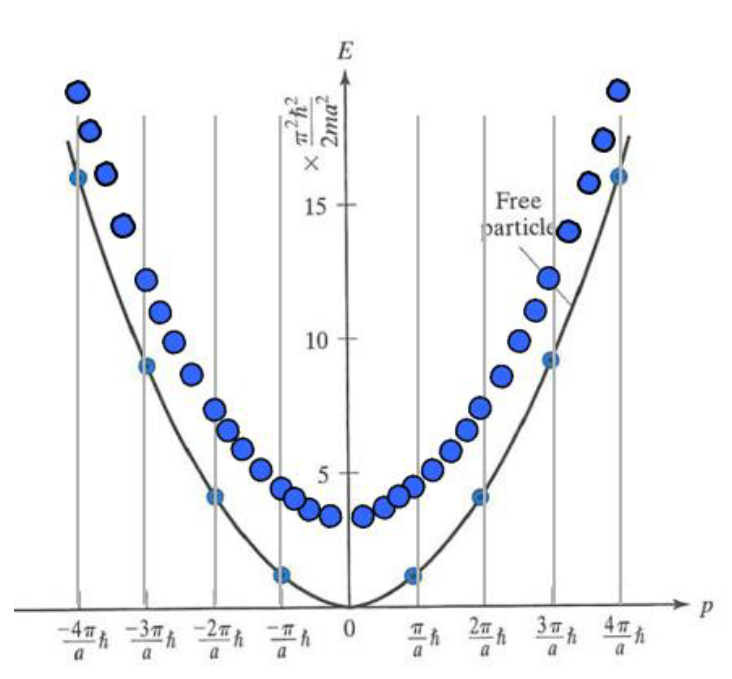

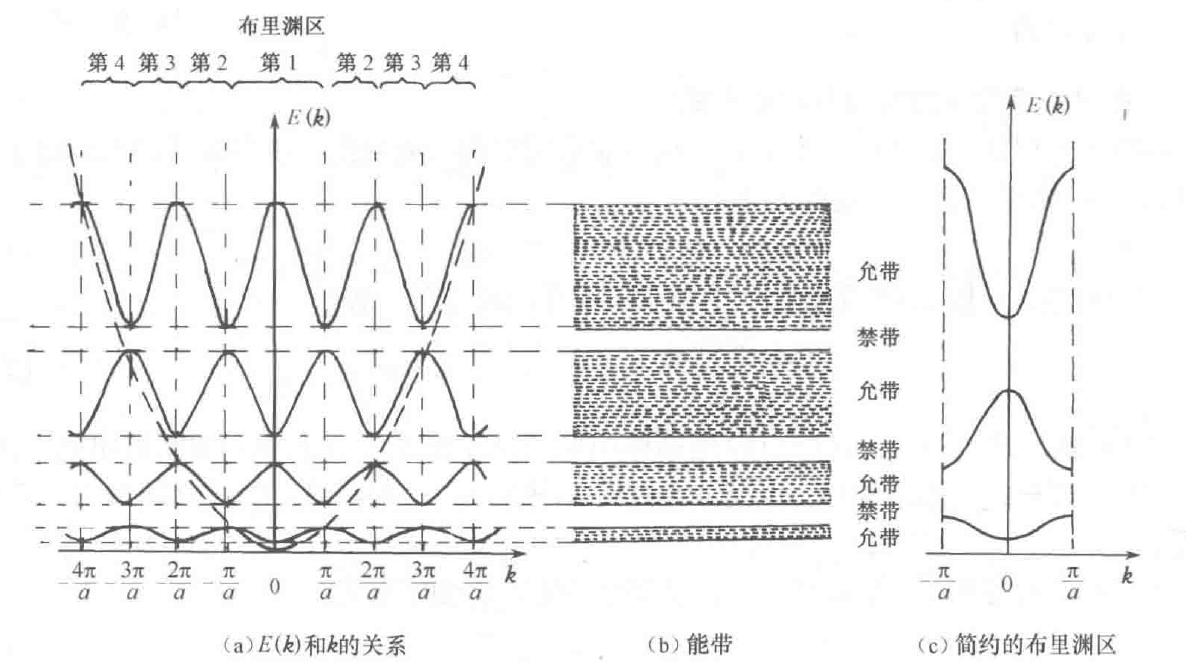

分别画出自由电子、一维受限电子、晶格电子的E-k关系示意图。

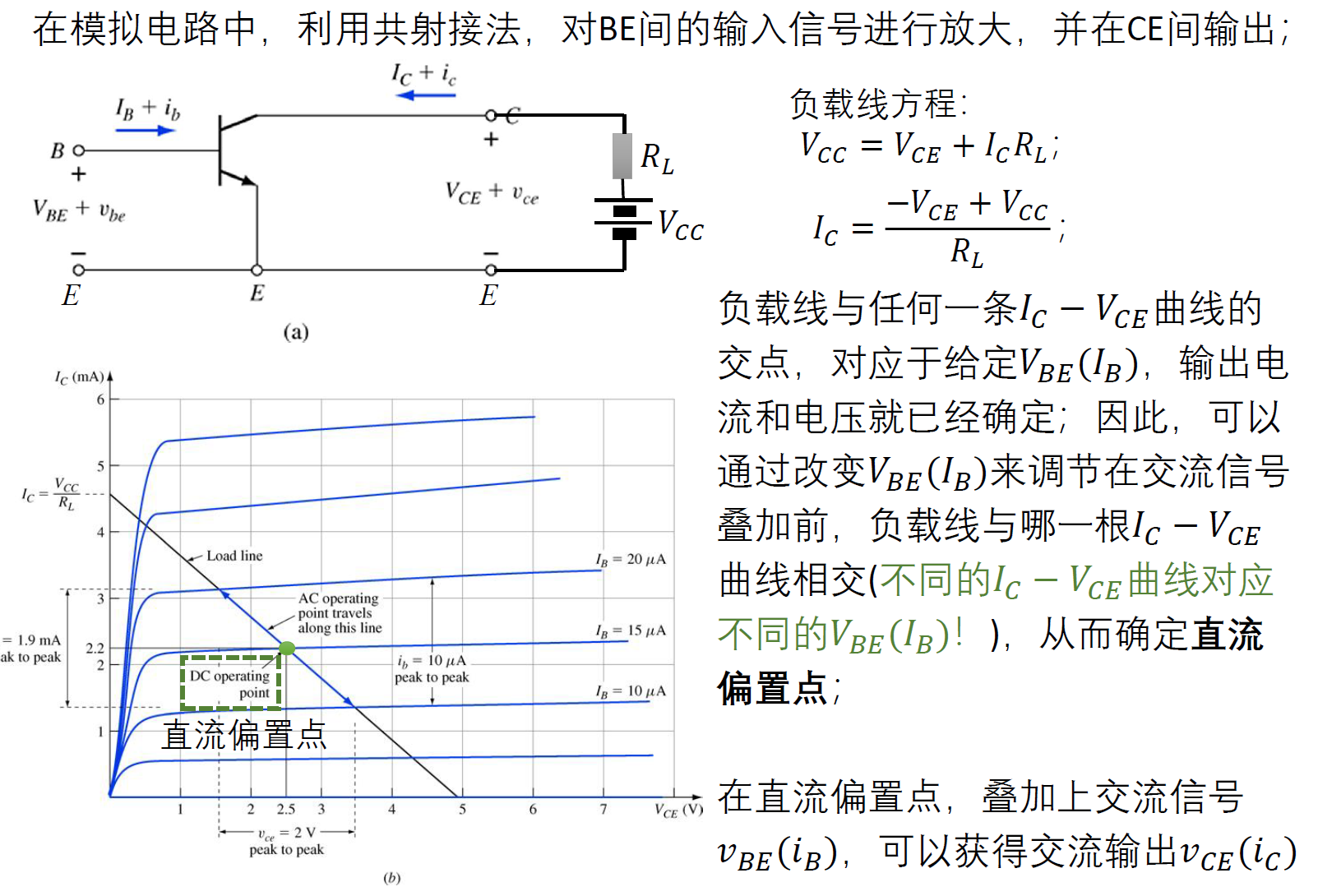

画出BJT共射极小信号模型电路图,写出三极的电流和偏压的关系式。

推导二维情况下的态密度公式。

$$S_{singlestate} = \frac{4\pi^{2}}{S}$$

$$S_{k} = \pi k^{2}$$

$$N=2 \times \frac {S_{k}}{S_{singlestate}} = \frac {S_{m^{*}}}{\pi \hbar ^ {2}} (E-E_{p})$$

$$S(E)=\frac{1}{S} \frac {dN}{dE}=\frac{m^{*}}{\pi \hbar^{2}}$$

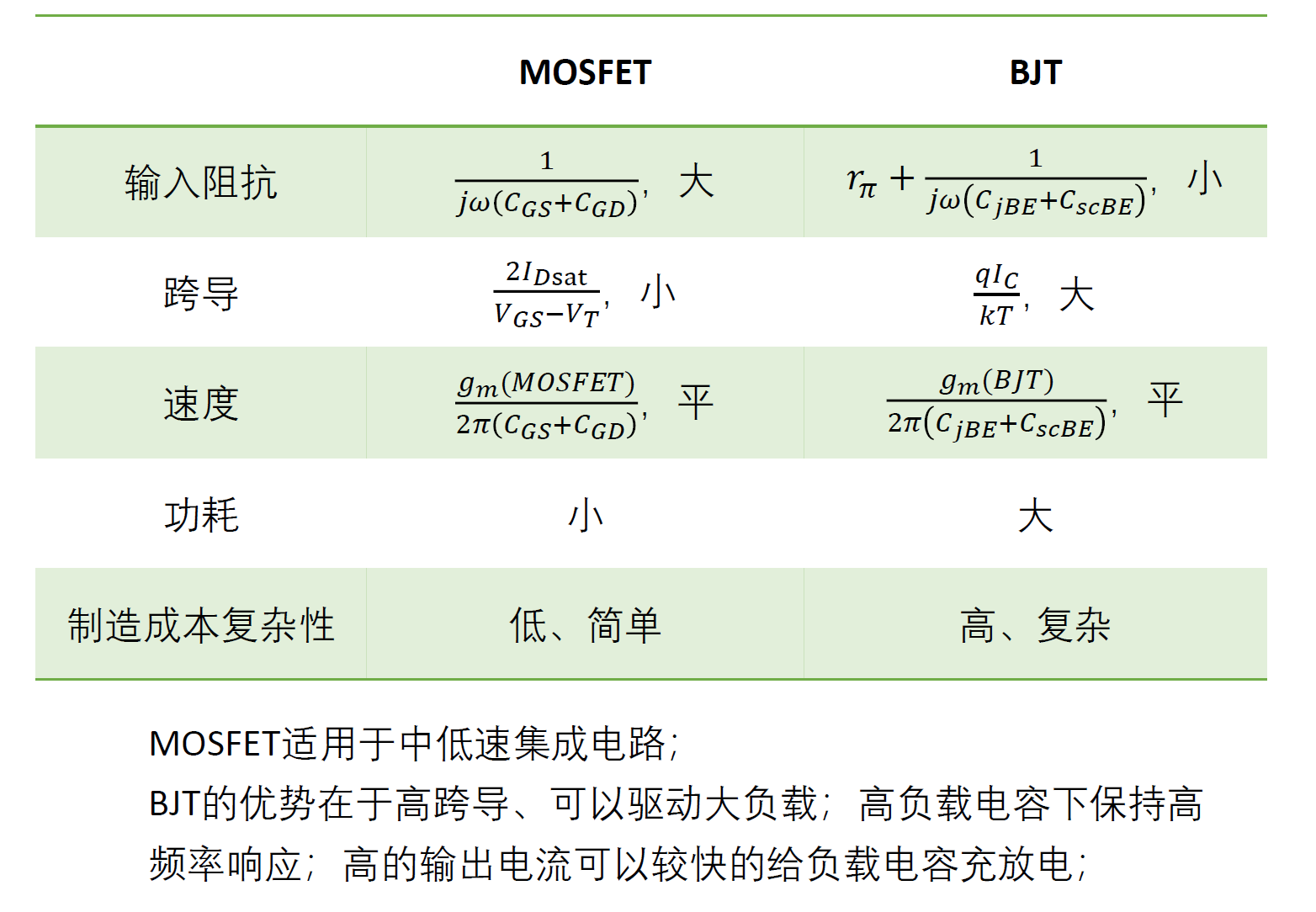

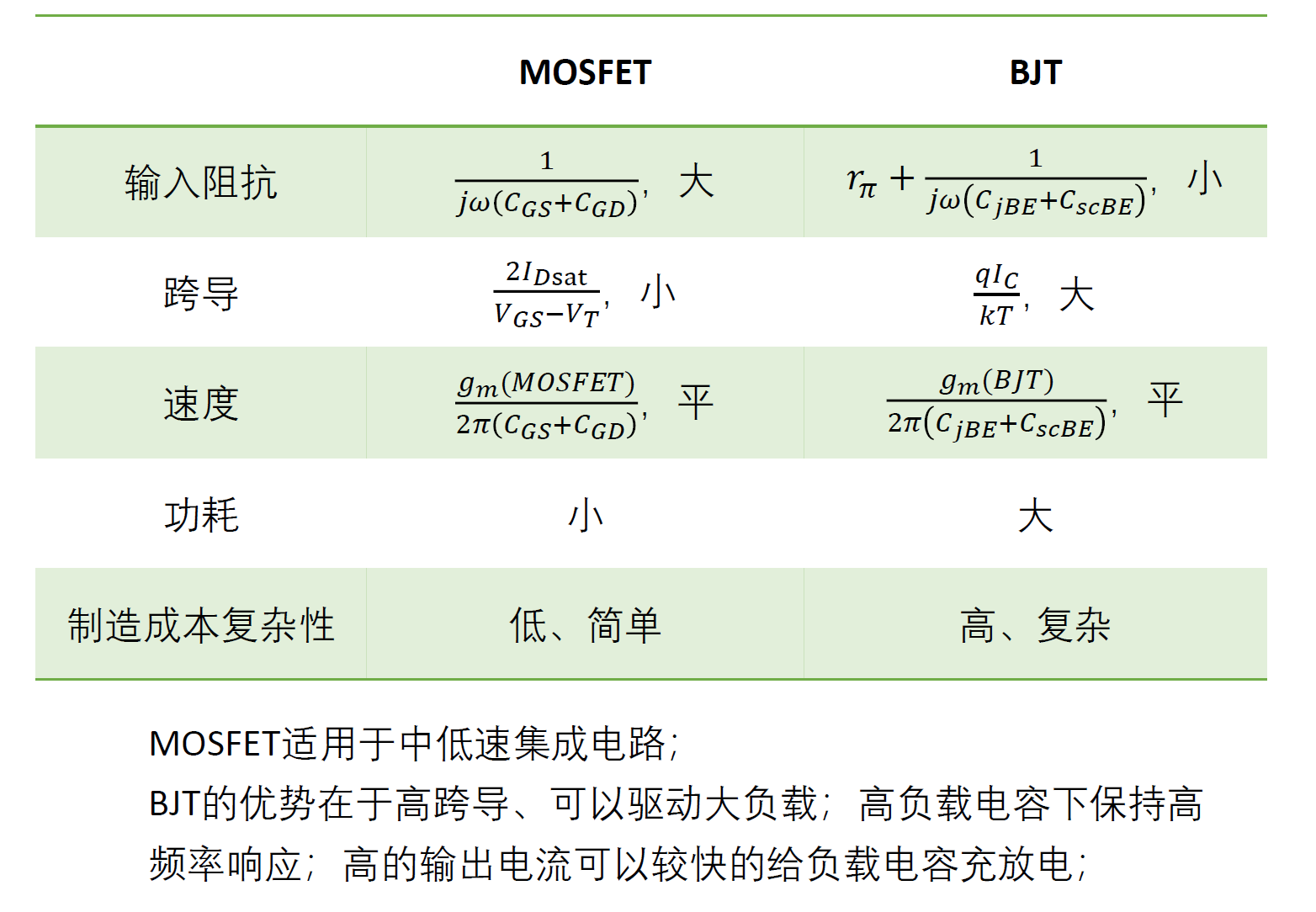

从开关速度、输入阻抗、跨导、工艺难度等方面比较BJT和MOSFET的性能。

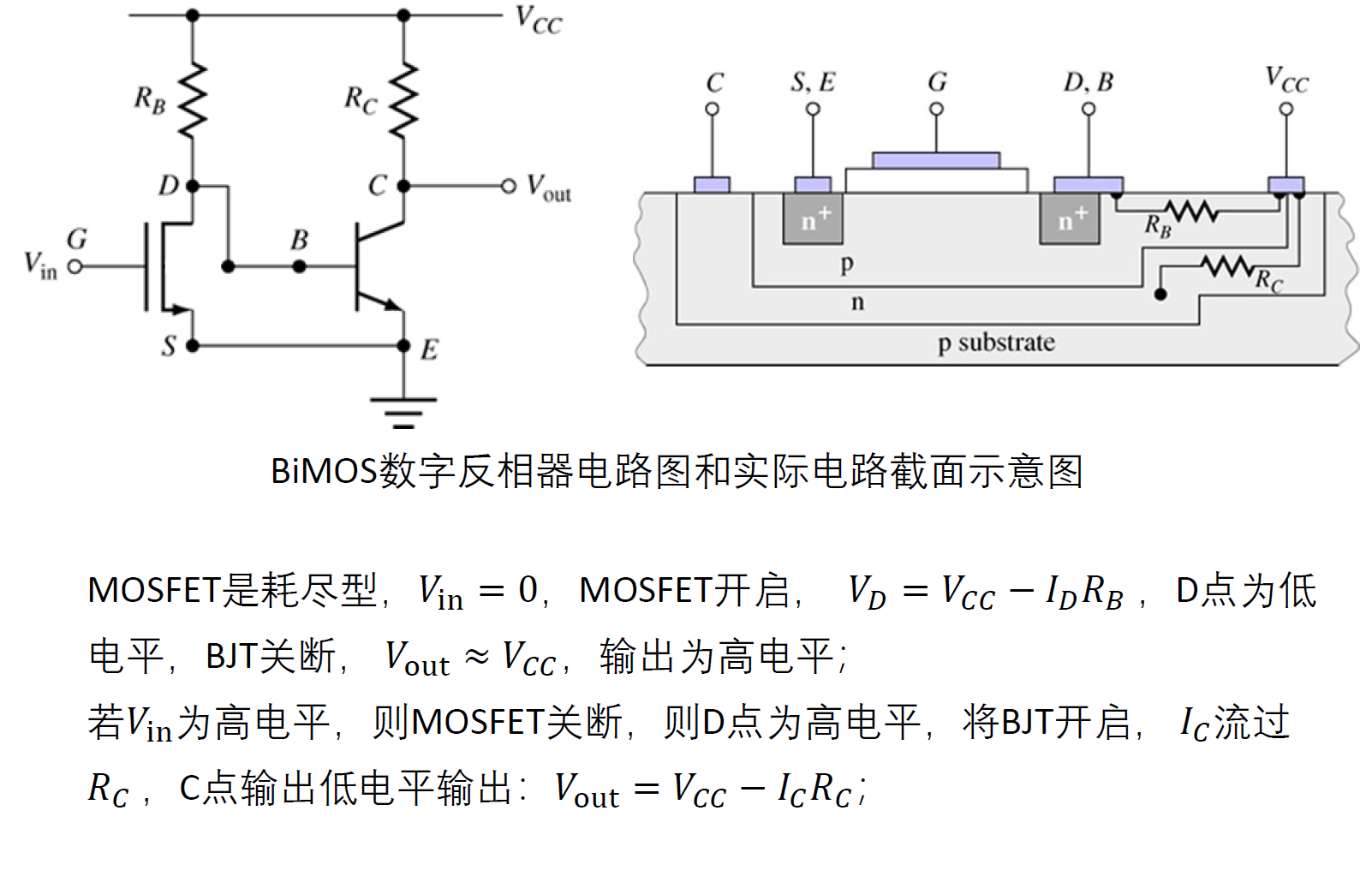

画出BiMOS反相器的电路图和器件结构剖面图。

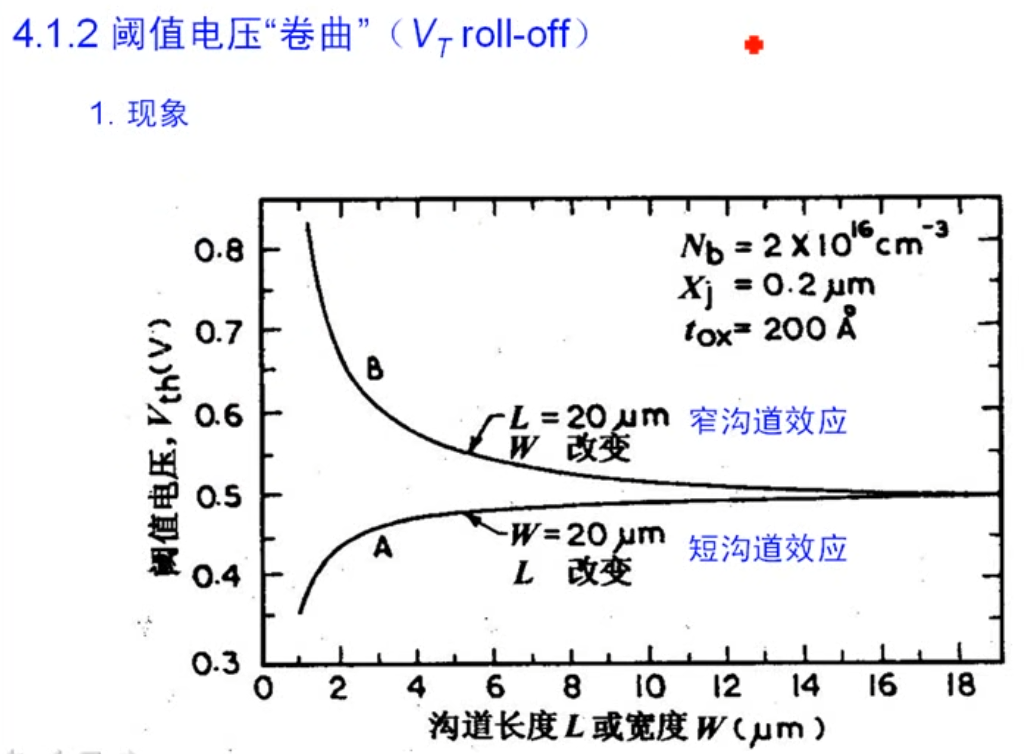

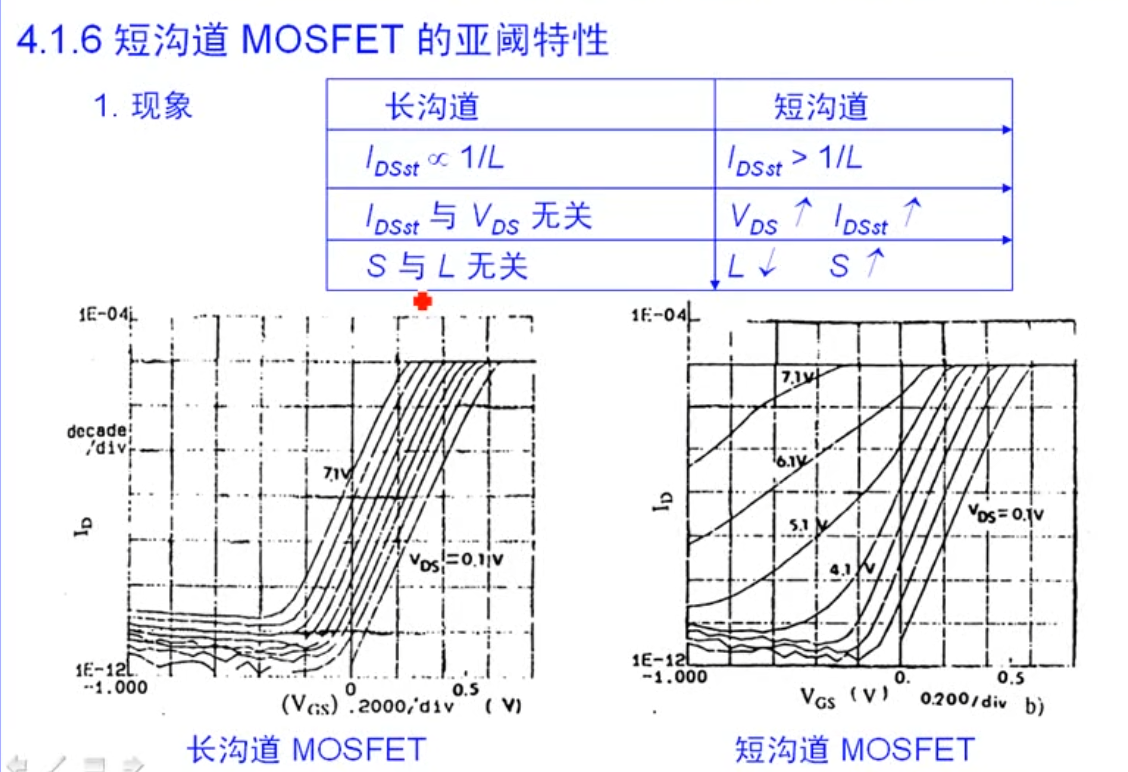

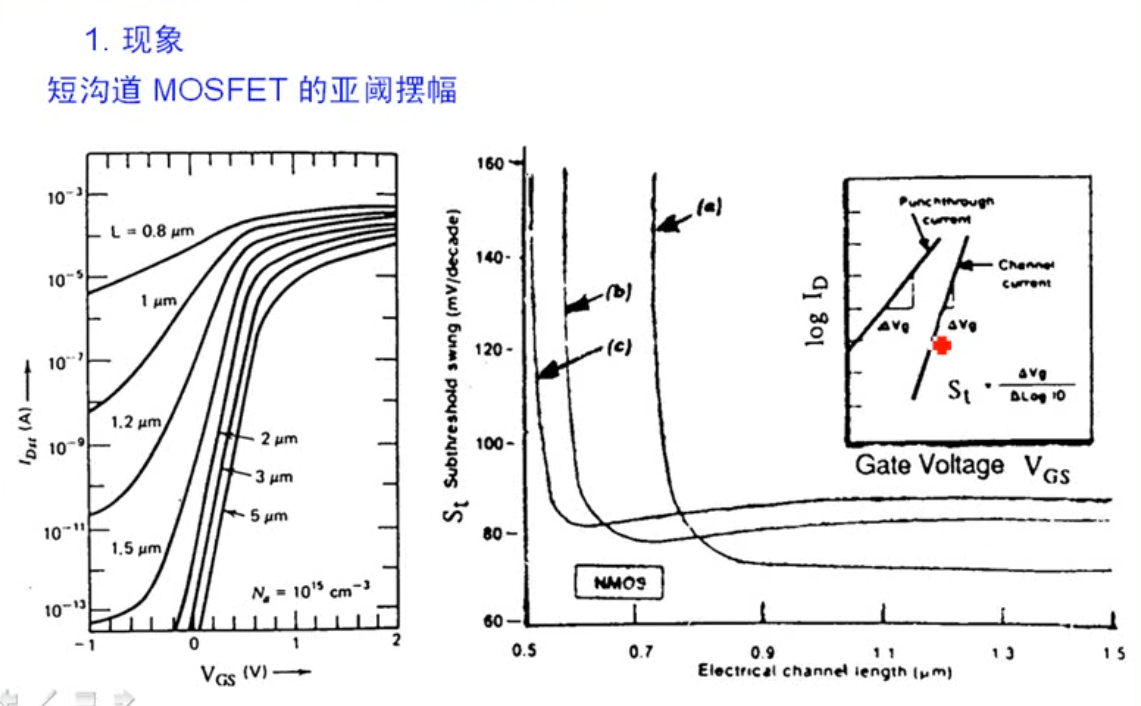

列举出MOSFET的短沟道效应,并说明相应的物理原理。

阈值电压roll-off、DIBL、速度饱和、亚阈值特性退化、热载流子效应

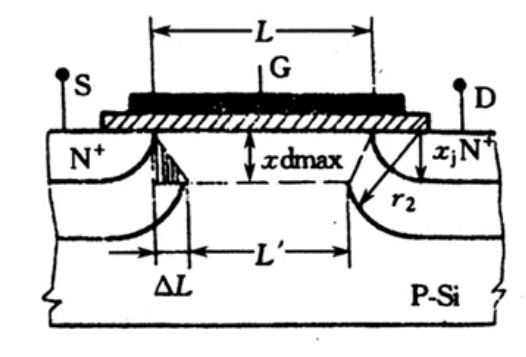

阈值电压roll-off

原因

面电荷密度下降,反型容易,Vth减小

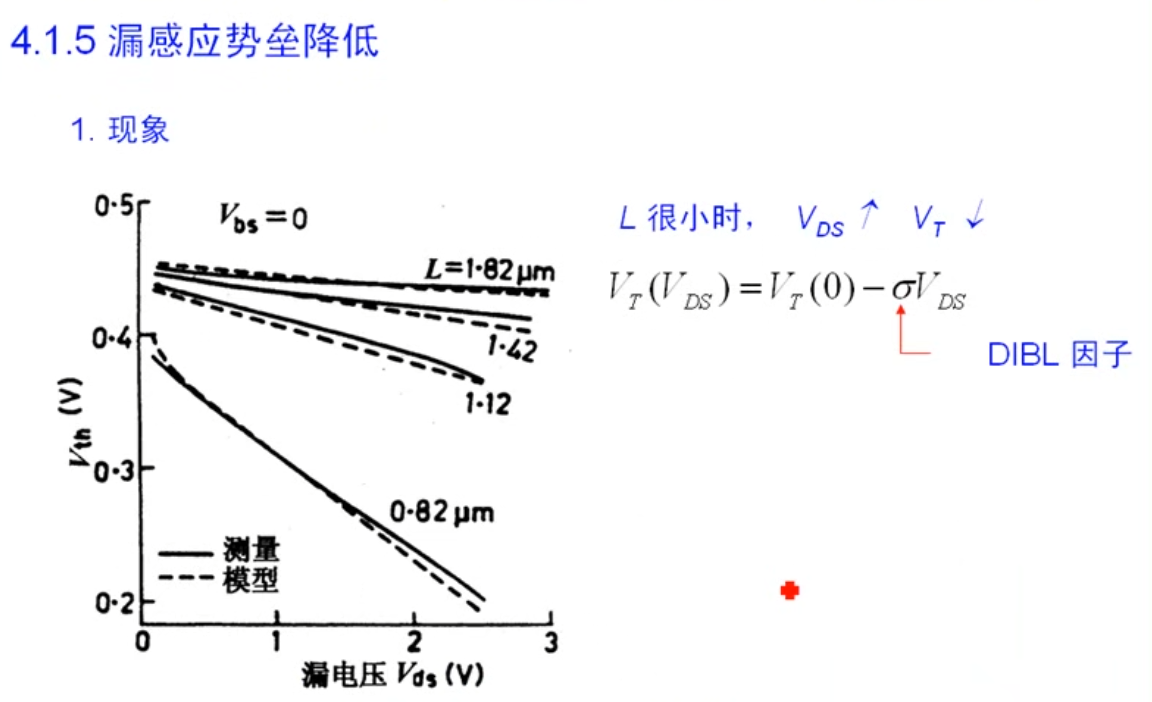

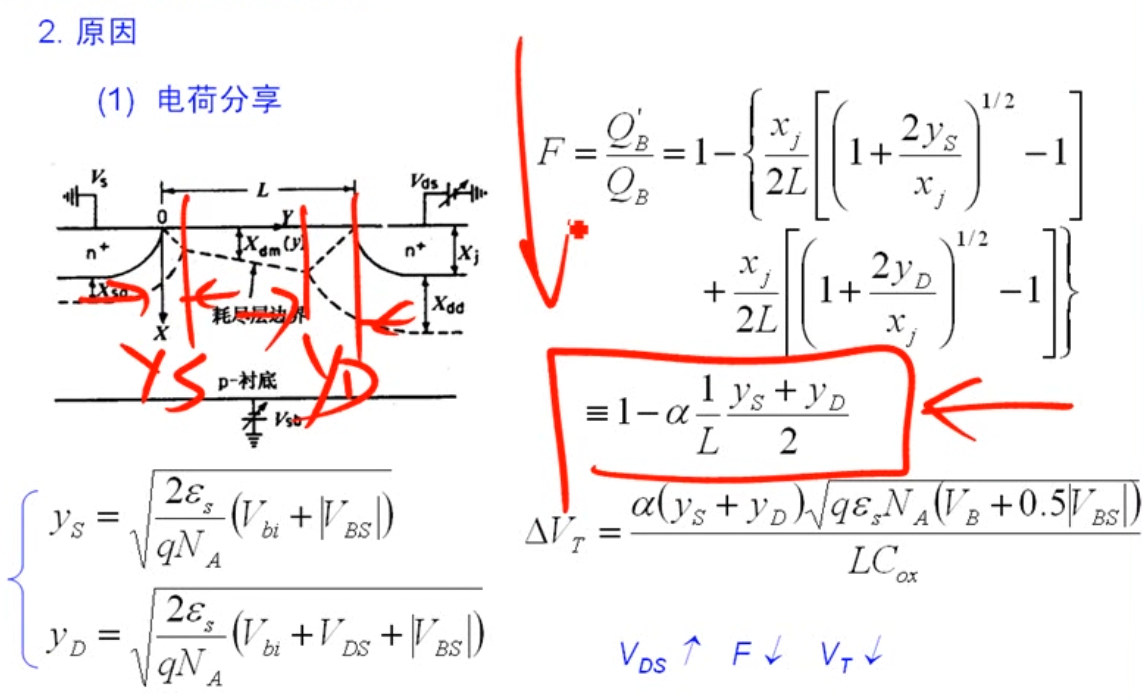

漏感应势垒降低DIBL

随着Vds增加Vth快速下降

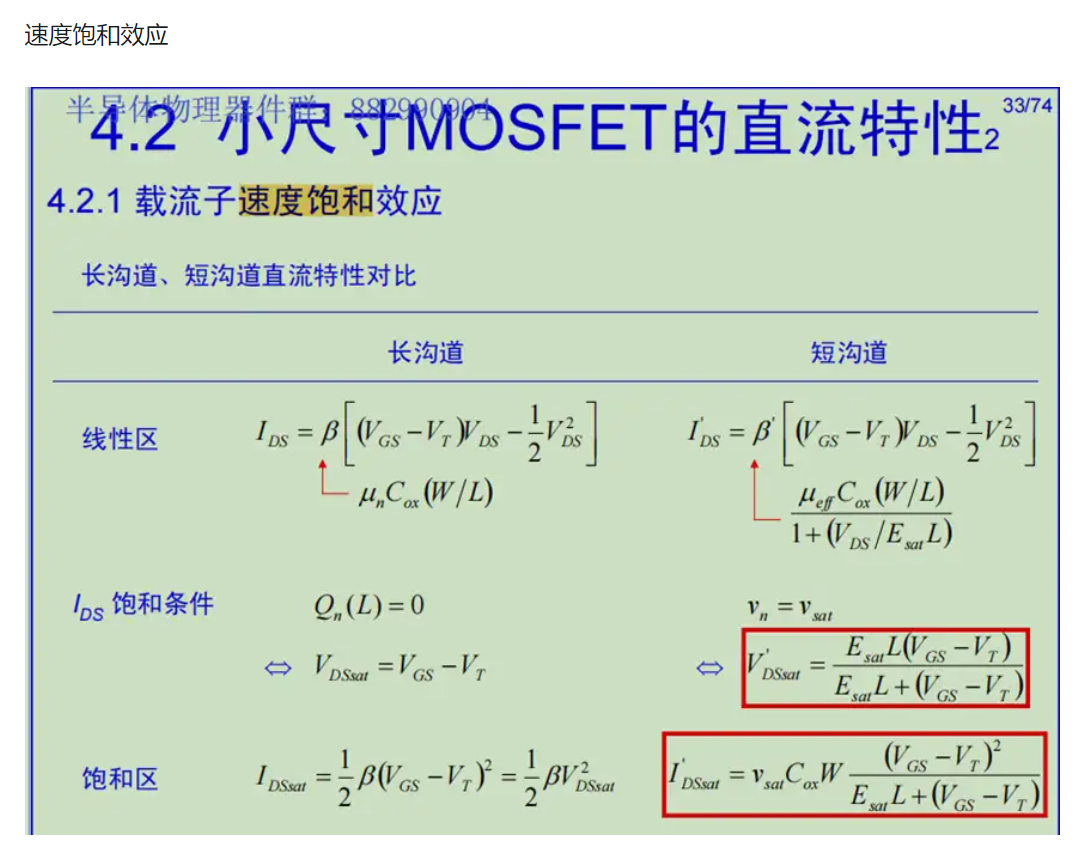

速度饱和

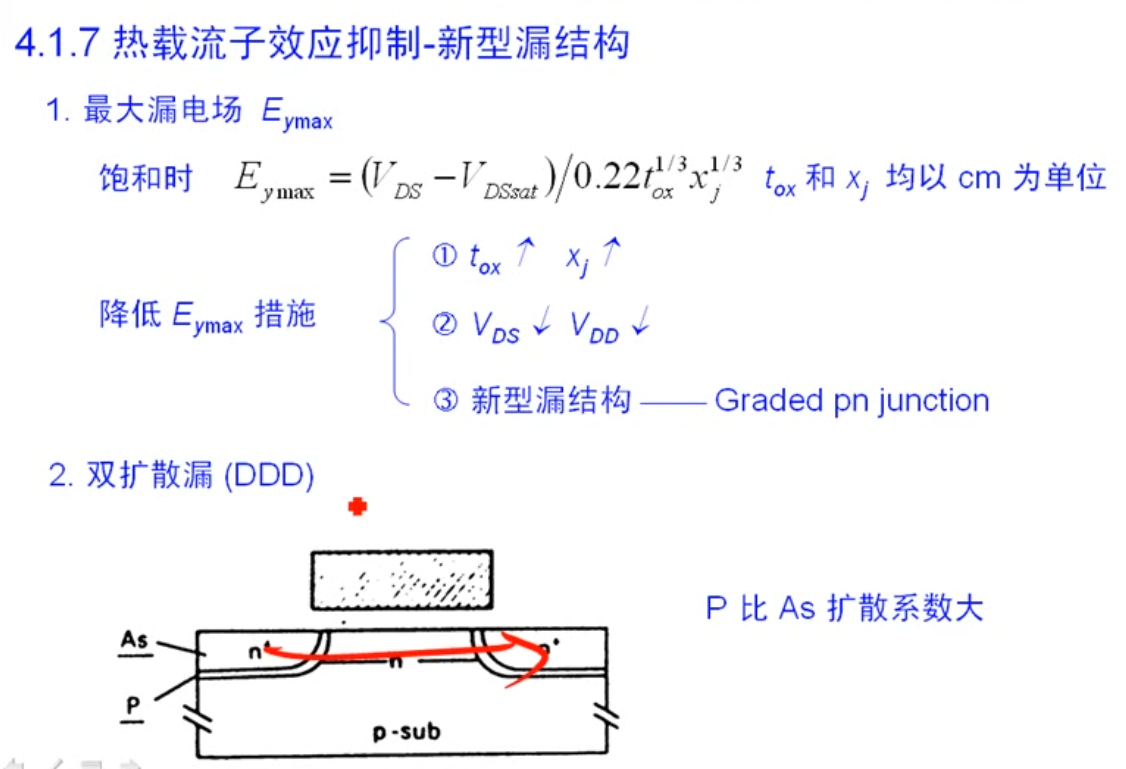

热载流子效应

大Ey会产生热载流子,要尽可能减小Ey

亚阈值特性

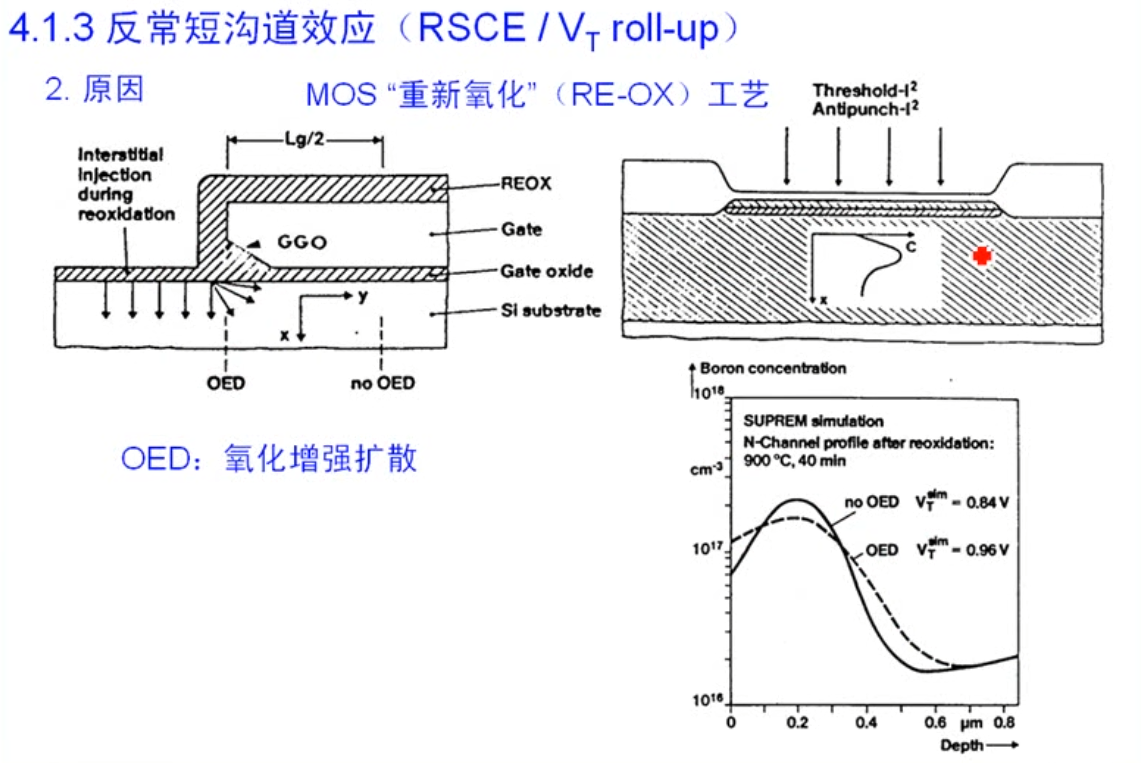

*反常短沟道效应,阈值电压roll-up

由于再氧化,导致衬底掺杂浓度重新分布,掺杂浓度减小,Vth增大

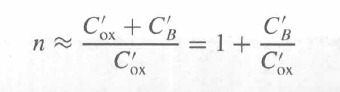

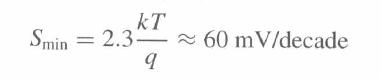

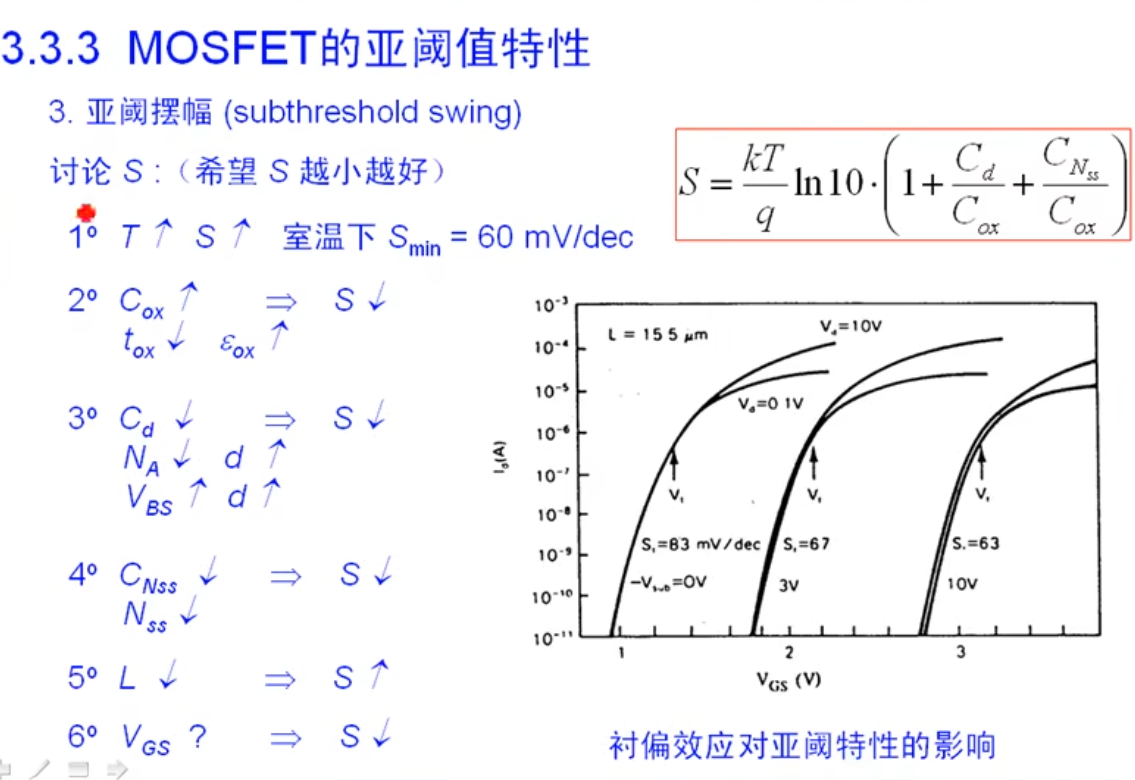

亚阈值摆幅的定义是什么?为什么要减小亚阈值摆幅?如何减小?

栅压要变化多少,才能使漏极电流有10倍的变化

计算npn型BJT的势垒电压、基区长度和β(类似教材P441 例9.1)

见习题

第二部分

异质结能带图

见4.1

异质结应用在光电探测二极管、发光二极管与制备 GaAs 基双极型器件的优势

- 调控pn结两侧电子空穴势垒高度;

- 光探测器、太阳能电池的宽带窗口;

- 形成电子空穴空间局域化;2DEG和2DHG,低维半导体物理

- 解决宽禁带半导体的单极性掺杂难题;

MOSFET的短沟道效应

见2.8

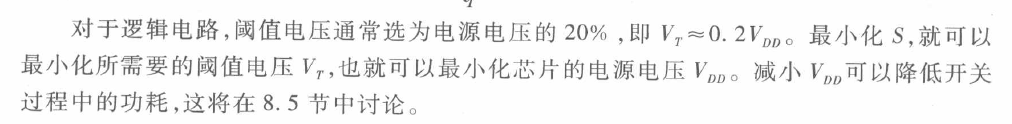

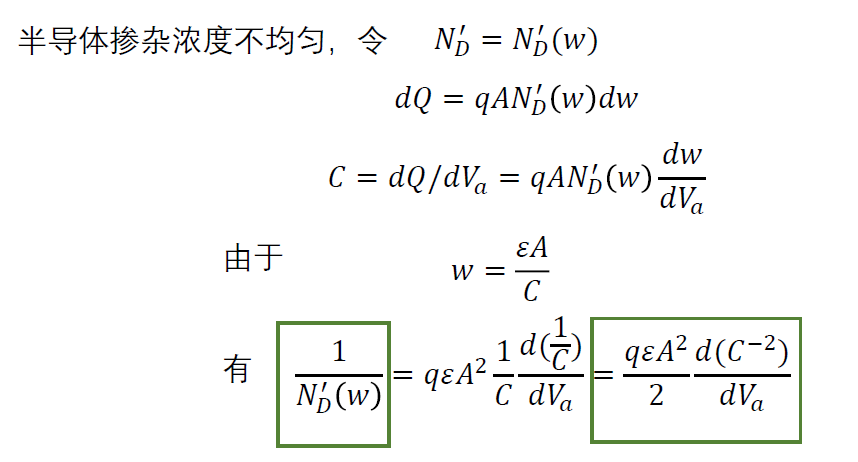

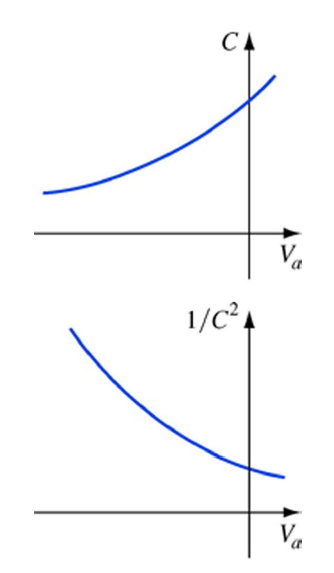

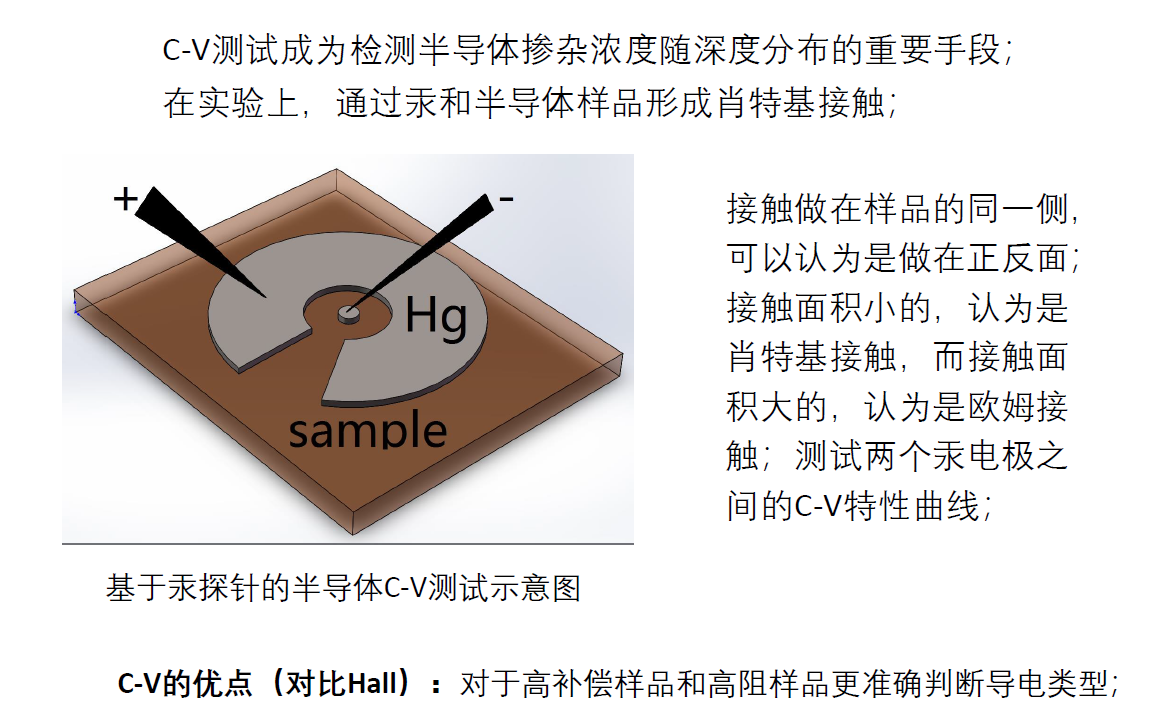

测量杂质浓度随深度变化的关系的实验方法

对一块pn结样品或肖特基结样品,做CV测试,可以从实验上测得内建电势差$V_{b i}$和材料的净掺杂浓度$N_{A(D)}$

$$C_{j}=A\left(\frac{\varepsilon q N_{A(D)}^{\prime}}{2V_{j}}\right)^{1/2}$$

$$\frac{1}{C_{j}^{2}}=\frac{2}{{A^{2}}\varepsilon q N_{A(D)}^{\prime}}\cdot\left(V_{b i}-V_{a}\right)$$

进一步考虑半导体侧非均匀掺杂的单边突变结或肖特基结的情形;

利用$w={\frac{\varepsilon A}{C}}$可以通过$w-C-V_{a}-N_{D}^{\prime}$的一一对应关系,求得$N_{D}^{\prime}(w)-w$的曲线,即净掺杂浓度的空间分布;

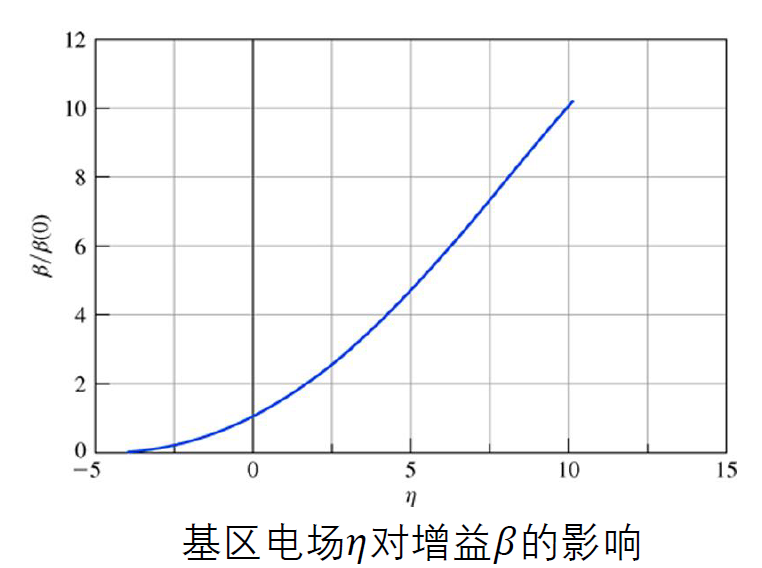

证明指数掺杂产生恒定电场

$$J_{p B}=q\mu_{p}p_{B}(x){\mathcal{E}}-q D_{p}\frac{d p_{B}(x)}{d x}$$ $$\frac{d p_{B}(x)}{d x}=\frac{q}{k T}p_{B}(x)\mathcal{E}$$ $$\mathcal{E}=\frac{k T}{q N_{A B}^{\prime}(x)}\frac{d N_{A B}^{\prime}(x)}{d x}$$ $$N_{A B}^{\prime}(x)=N_{A B}^{\prime}(0^{+})\mathrm{exp}(-x/\lambda)$$ $${\mathcal{E}}=-{\frac{k T}{q\lambda}}$$

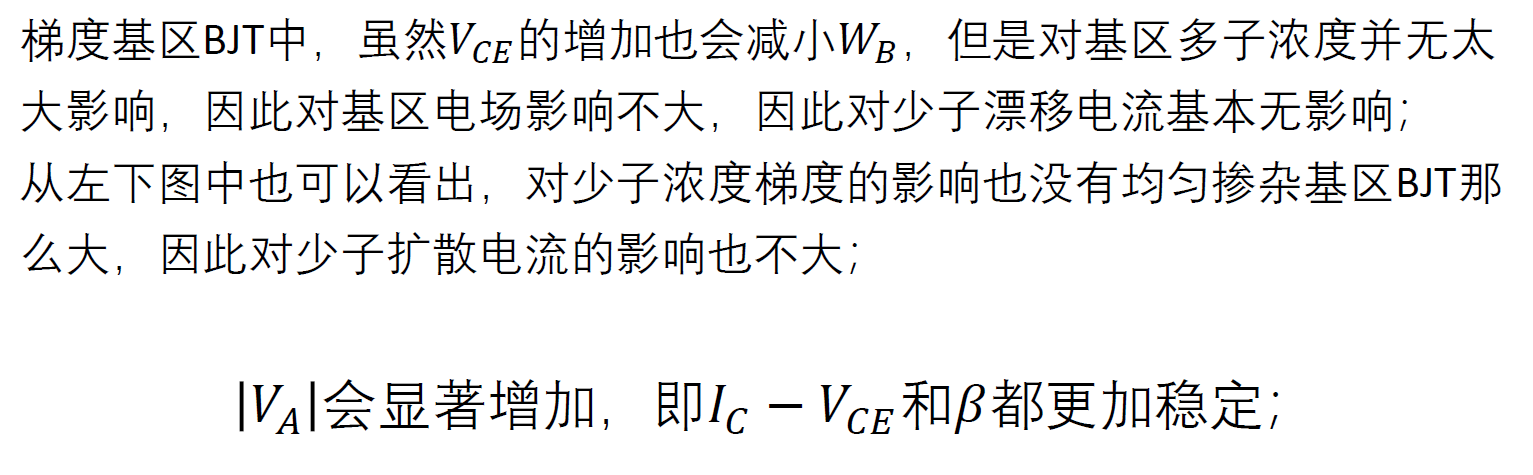

梯度掺杂的优势

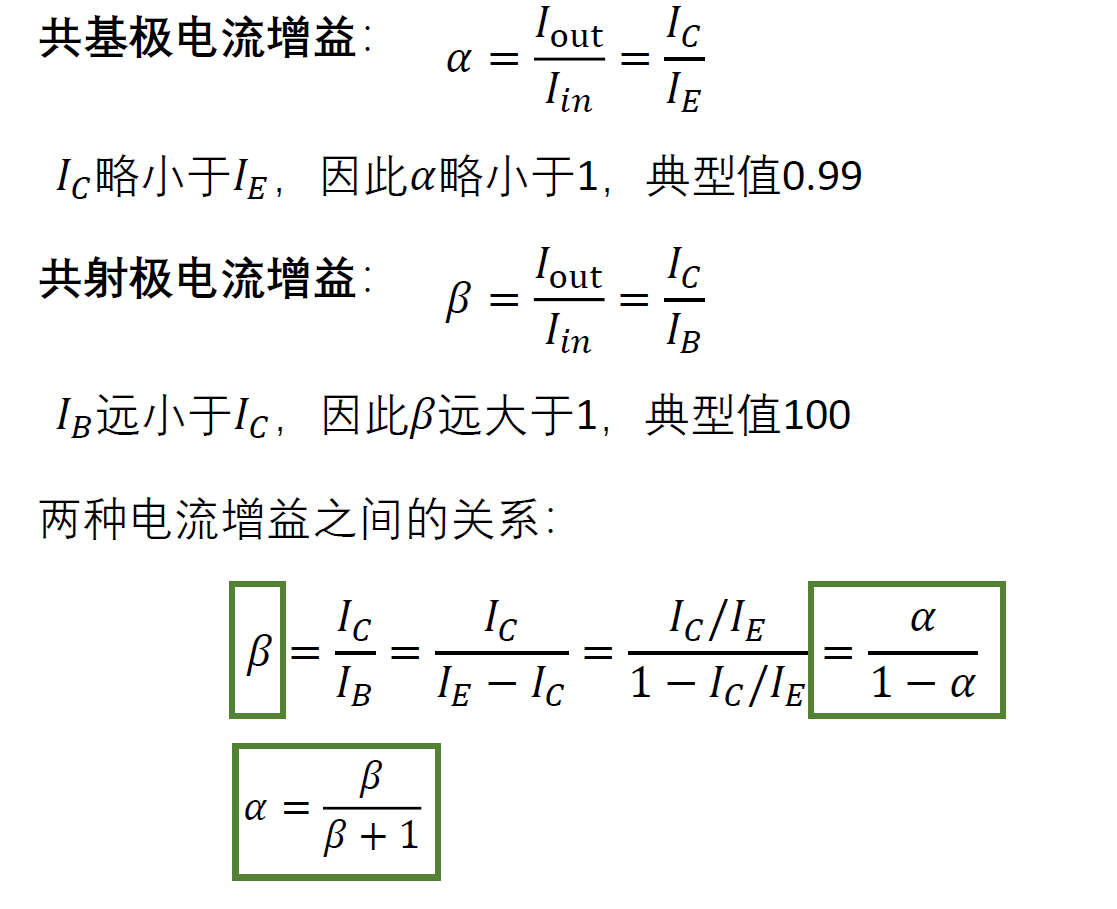

三极管的参数之间的数学关系

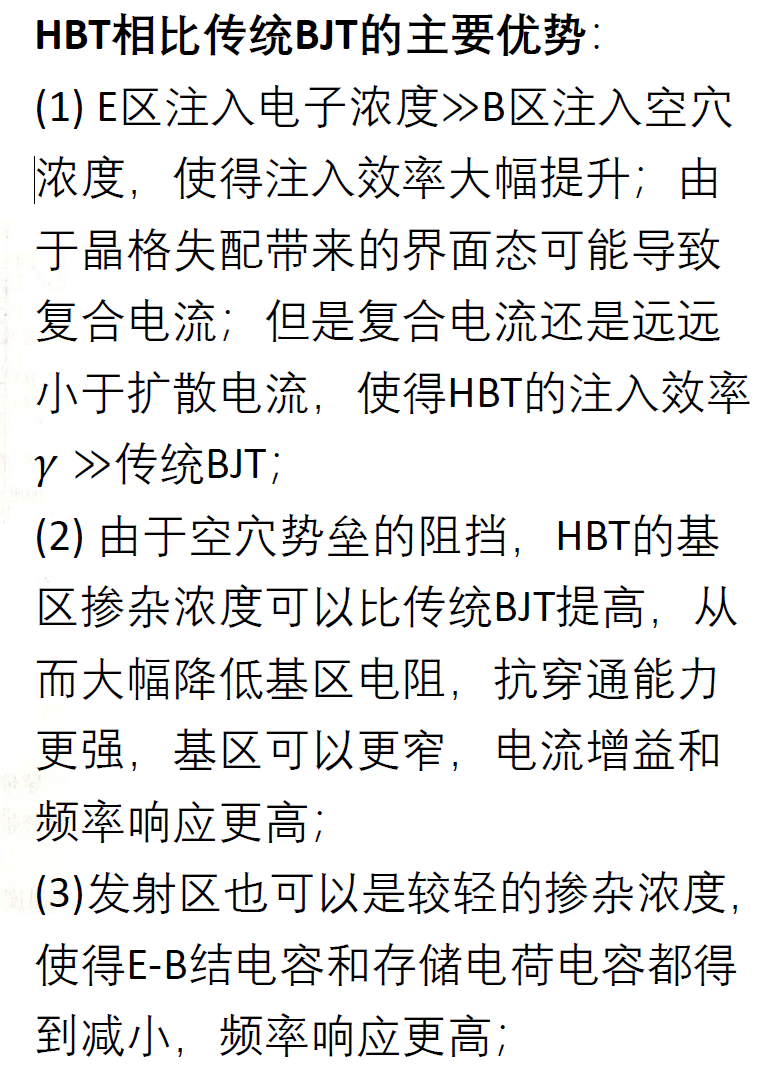

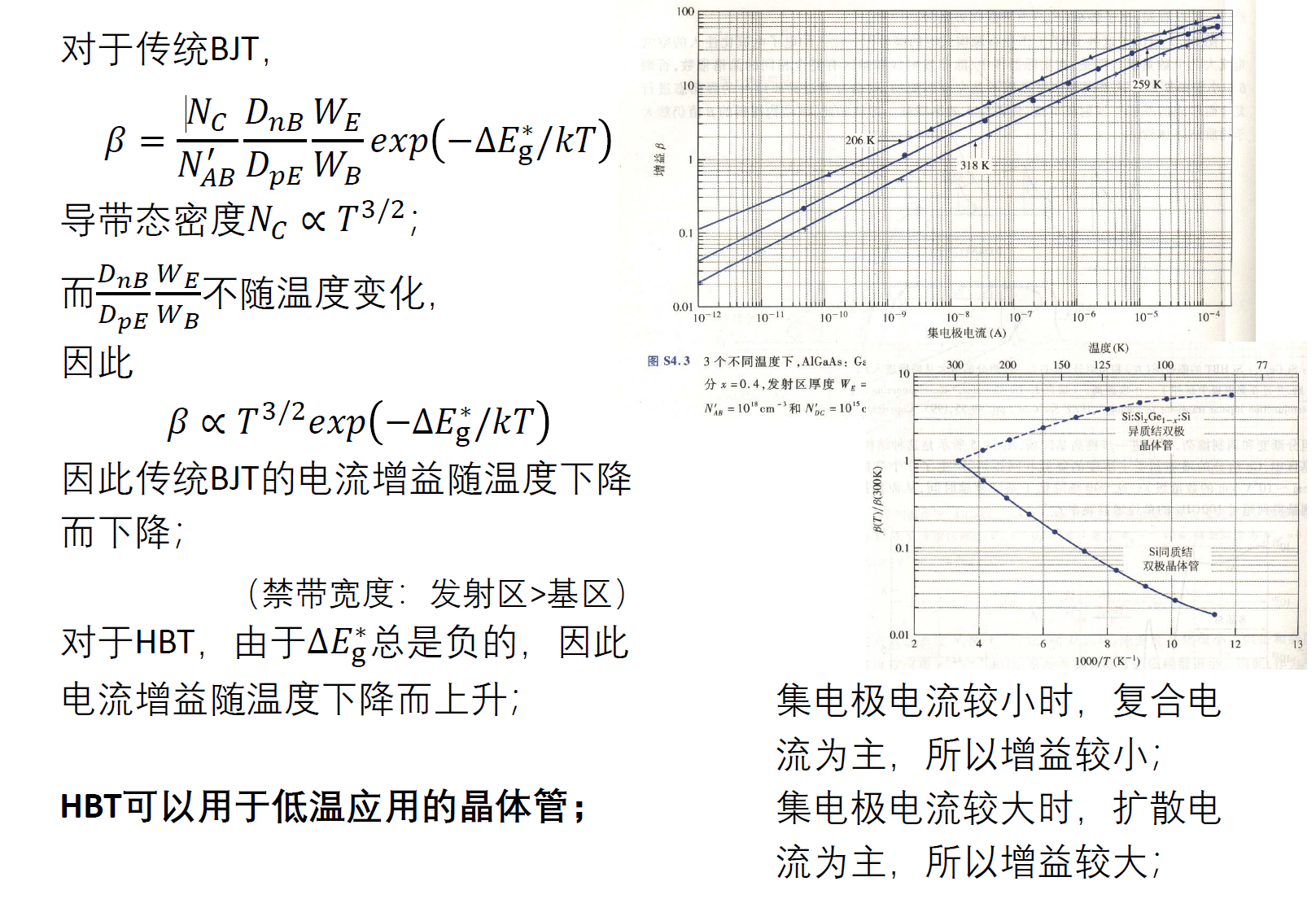

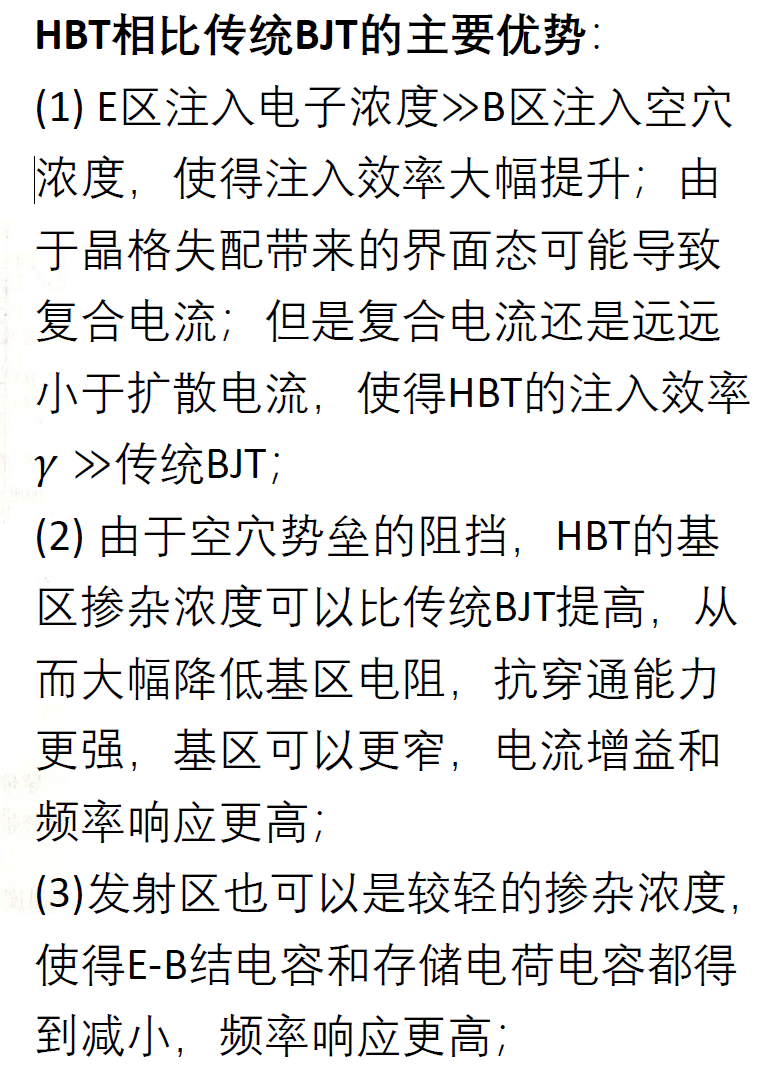

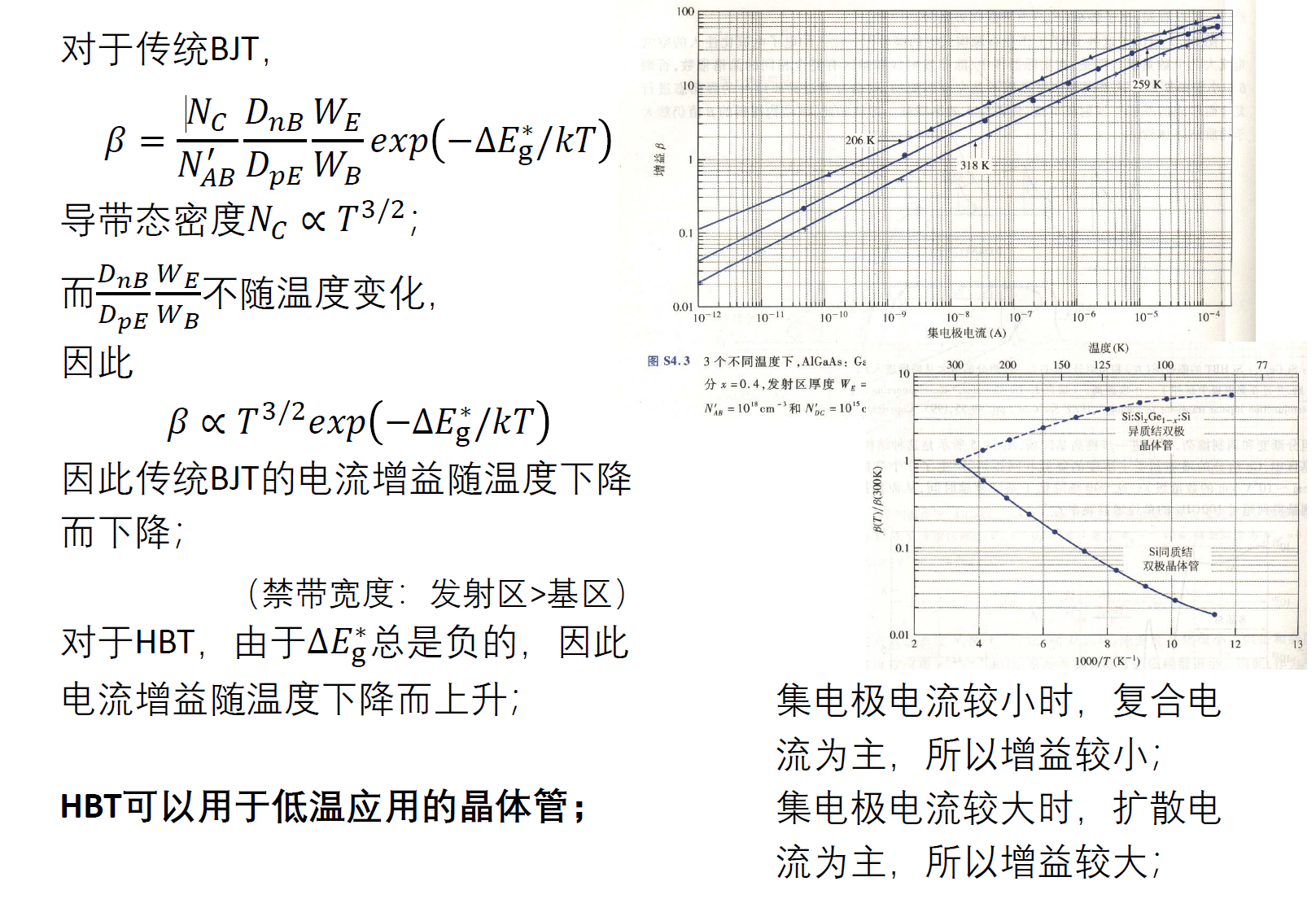

HBT相较于普通BJT的特殊性能

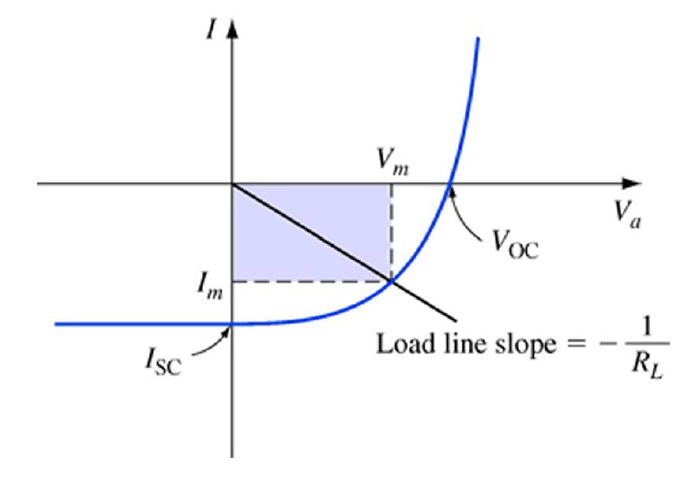

太阳能电池的工作曲线

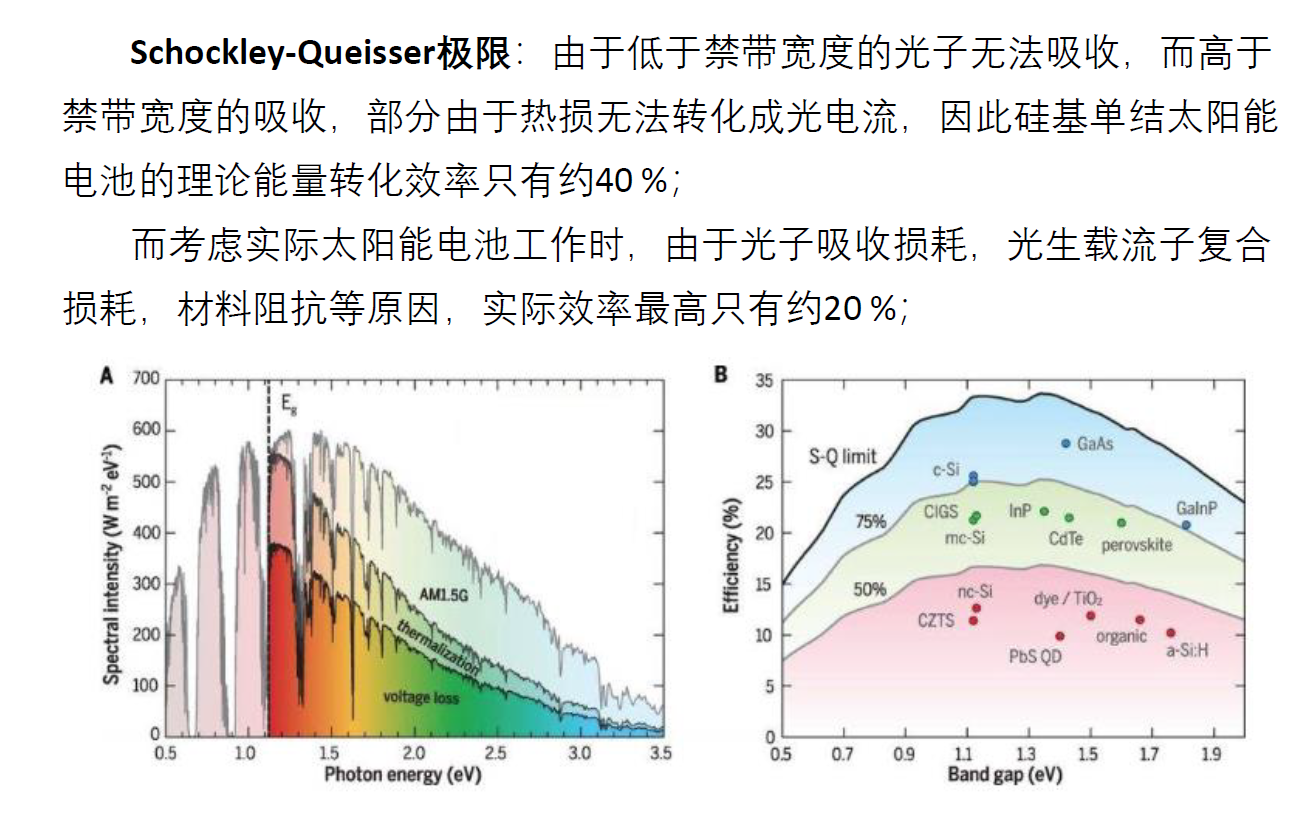

Schockley-Queisser 极限

清洁能源的特点

第三部分

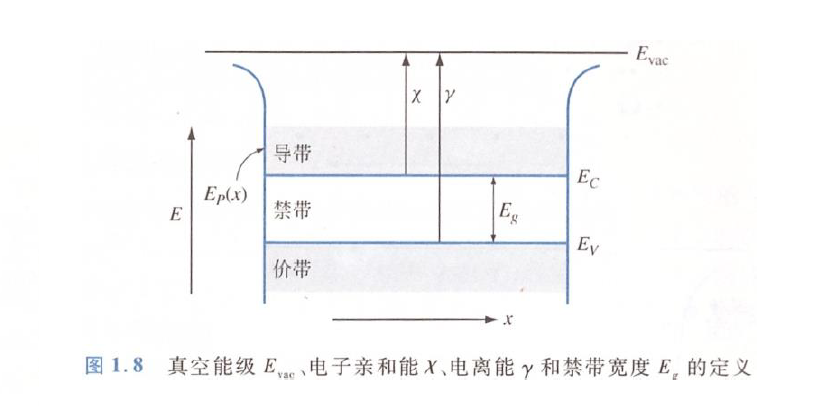

什么是电子亲合能模型?如何应用?总结用电子亲和能模型得到一个结的能带图的步骤。

电子亲和能模型(EAM),该模型假设半导体的材料参数直到冶金结处都是不变的,并且两种半导体的晶格常数相等。然后考虑两种材料的价带能量差导致的界面附近的电偶极层,对模型进行修正。我们还要考虑冶金结附近带中的能态(界面态)的影响。

能带图画法:费米能级拉平,真空能级连续,找到pn结接触点,两边都保证导带、价带与真空能级平行,中间突变连接

$$\chi=E_{v a c}-E_{c}$$

$$\gamma=E_{v a c}-E_{V}$$

$$W= E_{v a c}- E_{F}$$

$$E_{g}=E_{C}-E_{V}$$

$$\chi=E_{v a c}-E_{c}$$

$$\gamma=E_{v a c}-E_{V}$$

$$W= E_{v a c}- E_{F}$$

$$E_{g}=E_{C}-E_{V}$$

解释为什么在和半导体的低阻接触中,半导体的接触区域要做成简并的。(半导体物理知识)

欧姆接触不产生明显的附加阻抗,而且不会使半导体内部的平衡载流子浓度发生显著的改变。从电学上讲,理想欧姆接触的接触电阻与半导体样品或器件相比应当很小,当有电流流过时,欧姆接触上的电压降应当远小于样品或器件本身的压降,这种接触不影响器件的电流一电压特性。

半导体与金属接触时,多会形成势垒层,但当半导体掺杂浓度很高时,电子可借隧道效应穿过势垒,从而形成低阻值的欧姆接触。形成良好的欧姆接触有利于电流的输入和输出。

为什么在反偏时,pn 结的产生电流大于复合电流;而在正偏时,复合电流大于产生电流?

反偏时,势垒区内的电场增强,所以在势垒区内,由于热激发的作用,通过复合中心产生的电子空穴对来不及复合就被电场驱走了,因而势垒区内通过复合中心的载流子产生率大于复合率,具有净产生率。

正偏时,参与扩散的多子,在势垒区复合了一部分,注入的电子与空穴会穿过空间电荷区,空间电荷区存在过剩载流子。因此电子与空穴在穿越空间电荷区时有可能发生复合,并不成为少子分布的一部分。

请解释:为什么实际上并没有电流流入 MOSFET 的栅极?如果没有电流流入栅极,加在栅上的信号是怎样对晶体管其他部分的工作产生影响的? P309

MOSFET 就是一个压控电阻,这个电阻处于源-漏之间,可以通过控制提供电导的沟道载流子数来控制源-漏间的沟道电导。在 MOSFET中,这种控制是通过调节栅压,控制半导体能带弯曲实现的。栅压迫使导带底更加靠近或远离费米能级。

因为在栅和源,沟道、漏之间有一层绝缘的氧化层,所以电流不会流入栅极。栅压在氧化层中感生电场,这个电场进而影响半导体的能带。赋予场效应晶体管这一名称的这个电场,就是由栅压感生的电场。对于MOSFET ,是指氧化层上的电场。

内建电势差一部分降在氧化层上,一部分降在半导体上。这时,半导体表面有一个耗尽区:多子耗尽区。

用自己的话解释为什么源和漏之间的电流(流量)会随着漏源之间电势差的增大而饱和。 P309

随着Vs增大,靠近漏端的纵向电场El增大较快,而靠近源端的纵向电场增大较慢(电场正比于导带底的斜率),并且所增加的漏电压绝大部分降在漏端附近。也就是说,随着Vds增大,靠近源端的纵向电场变化很小。最终,在某一个Vds值,源端电场达到一个极限值。由于沟道一端的电流必须和另一端的电流相等,所以电流被限制在源端电场所能提供的水平。当电场El(y =0)达到饱和时,电流也达到饱和。

以长沟模型为例,用文字来总结推导FET ID-VDS特性的步骤。 P310

用文字说明,加在栅上的电压如何使沟道表面的材料由 p 型变成 n 型。

外加正栅压的作用是使沟道能量(导带底)降低,使导带底向下弯曲,更接近费米能级。和以前相比,现在的表面是更强的n型,即更强的反型。沟道中有了更多的电子,电导增大了。

当表面处禁带中央能量值降到费米能级以下时出现反型层,当表面处少子浓度超过体内多子浓度的时候进入强反型状态。

为什么减小亚阈值电流很重要?为此,在设计过程中要做哪些折衷考虑。

静态功耗是由于漏电流引起的,低功耗设计的需求:提高设备的可靠性(散热)、降低成本……

亚阈值电流主要是扩散电流

提高上栅氧化层电容Cox,降低耗尽层电容……FDU-P54-3.3.3 改善SS(subthreshould swing)的6个方法

列出短沟道效应,解释每一种效应的物理本质以及对 FET 的 ID-VDS特性的影响。(最重点的内容)

见2.8

考虑 MOSFET、HFET、MESFET 和 JFET,确定每一种器件的控制电场存在的区域。每种器件的控制机理是什么(即穿过氧化层的电场,改变耗尽层的电压等)。P364

HFET异质结场效应晶体管

在衬底上外延生长p型GaAS作为体区,通过栅加电场控制位于表面的沟道。

HFET 的工作原理和MOSFET类似。对于图8.24所示的器件,热平衡时,沟道导带在费米能级之上,沟道中并没有很多的电子。因此,沟道没有明显的电导。当栅上加正电压时,沟道一边的能带图向下移动,沟道导带底将接近费米能级,使沟道填充电子并导电。较大的负栅压将使沟道耗尽。

采用 HFET结构的优点是高速。未掺杂的AlGaAs 和轻掺杂的p型GaAs中几乎不存在对沟道电子的电离杂质散射。由于电子散射减小,所以电子迁移率提高,可以实现高速器件。

MESFET金属-半导体场效应晶体管Metal-Semiconductor FET 微波、高速、大功率和低噪音等性能

MESFET是一种由Schottky势垒栅极构成的场效应晶体管。它与p-n结型栅场效应晶体管相比,只是用金属-半导体接触势垒代替了p-n结栅,则热稳定性较差、漏电流较大、逻辑摆幅较小、抗噪声能力较弱;但是金属-半导体接触可以低温形成,而且不仅可用Si,而且也能采用GaAs材料来制造出性能优良的晶体管。

对于InP这种化合物半导体,由于其Schottky势垒高度较低,难以制作出性能良好的MESFET。InP可以制作出MOSFET,而难以制作出MESFET;GaAs可以制作出MESFET,但难以制作出MOSFET(由于GaAs的表面态密度太大)。

MESFET和前面讨论的FET的不同之处在于:该器件的沟道并不是直接形成在半导体表面,而是在表面之下。肖特基势垒引起的耗尽区中没有载流子,因此是绝缘的。由此看来,耗尽区的作用有些类似于MOSFET中的栅绝缘层。

两个耗尽区(肖特基结、沟道和半绝缘衬底之间)之间即为沟道宽度,外加栅压控制肖特基结的耗尽区宽度从而改变沟道宽度,drain加正压的时候肖特基势垒反偏程度大于source端,沟道厚度小,载流子速度大。

MESFET的工作原理与JFET基本相同, 但是有两点差异:

a)在短沟道(0.5~2μm) GaAs-MESFET中, 速度饱和模型能较好地描述I-V特性(虽然饱和机理是由于谷间跃迁而引起的速度饱和,但与Si和SiC等的MESFET相同,都将产生偶极畴并使电流饱和);

b)对于栅长<0.5μm的GaAs-MESFET, 由于GaAs中电子的能量弛豫时间»动量弛豫时间,则电子的输运将是瞬态的, 有明显的速度过冲效应(对短沟道Si器件, 无明显的速度过冲)。

HEMT由于其栅极往往是Schottky势垒栅,故实际上也可以看成是一种性能特别优良的超高频、超高速的MESFET。

JFET 结型场效应晶体管(Junction Field-Effect Transistor,JFET)

对于结型场效应晶体管(JFET),最常见到的是耗尽型JFET(D-JFET),即在0栅偏压时就存在有沟道 的JFET;一般,不使用增强型JFET(E-JFET)——在0栅偏压时不存在沟道 的JFET。这主要是由于长沟道E-JFET在使用时较难以产生出导电的沟道、从而导通性能不好的缘故。不过,由于高速、低功耗电路中应用的需要,有时也需要采用E-JFET。

JFET导电的沟道在体内。耗尽型和增强型这两种晶体管在工艺和结构上的差别主要在于其沟道区的掺杂浓度和厚度。D-JFET的沟道的掺杂浓度较高、厚度较大,以致于栅pn结的内建电压不能把沟道完全耗尽;而E-JFET的沟道的掺杂浓度较低、厚度较小,则栅pn结的内建电压即可把沟道完全耗尽。

但是,对于短沟道E-JFET,情况则有所不同,因为这种晶体管的漏极电压可以作用到源极附近,使得沟道中的势垒降低,所以能够形成导电沟道。这种E-JFET从本质上来说也就是静电感应晶体管。

在导电机理上与JFET相同的场效应晶体管就是Schottky栅极场效应晶体管(MESFET),这里只是用金属-半导体接触的Schottky结代替了p+-n结作为栅极。

另外还有一种场效应晶体管,就是高电子迁移率晶体管(HEMT),这种器件在结构上与MESFET类似,但是在工作机理上却更接近于MOSFET。

器件制作完成后,如何控制 MOSFET 的阈值电压。P388

离子注入是在器件制造过程中调节阈值电压的技术。

器件制作完成后——改变衬底和源之间的偏置电压。调节沟道和衬底之间的耗尽区宽度。

解释为什么在较大的VGS下ID-VDS特性不是直线。

一些东西

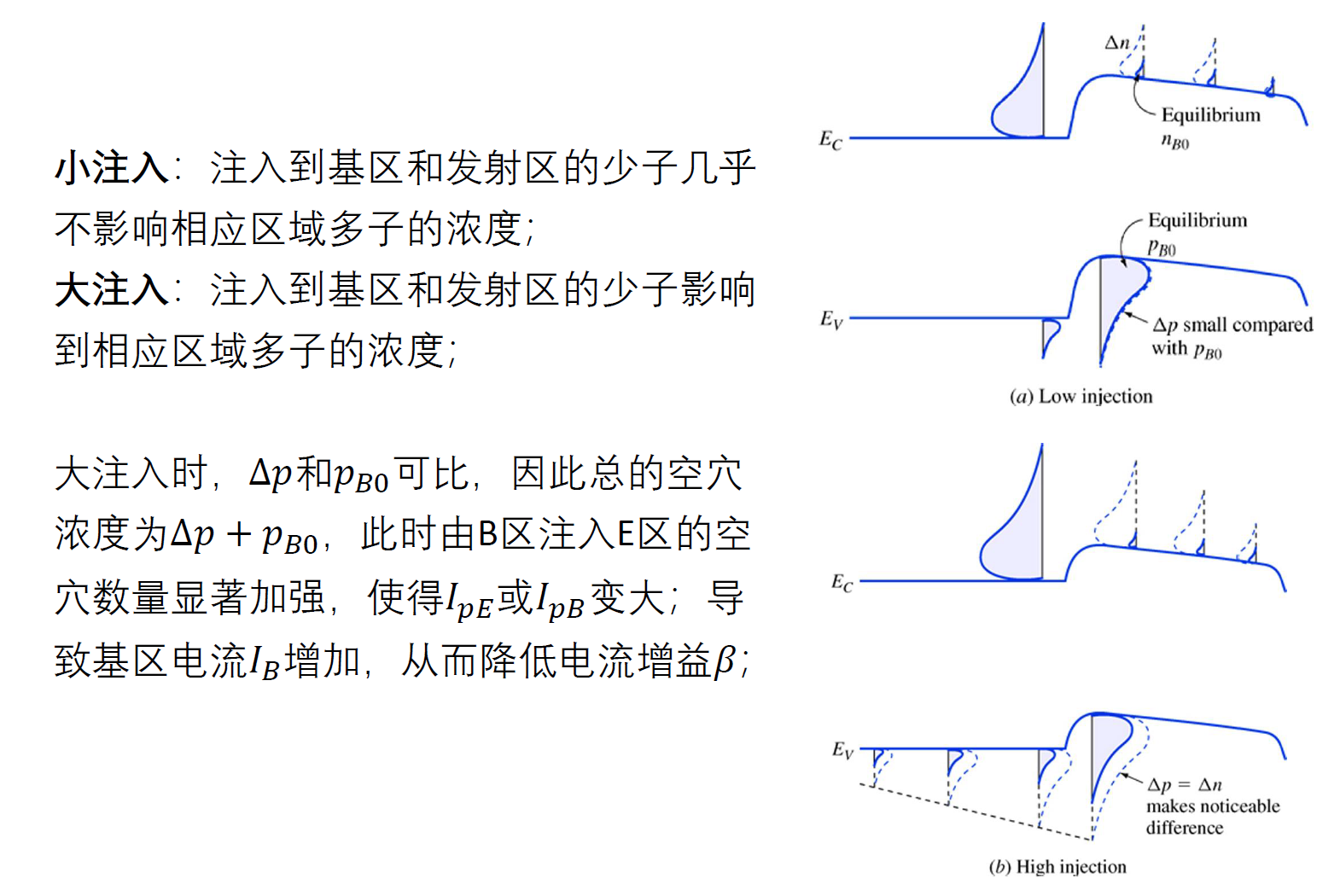

BJT雪崩

$$M={\frac{1}{\gamma}}=1+\frac{1}{\beta}$$

大注入效应

由于B区空穴浓度显著提高,Ipe、Ibe增加,空穴电流增加,β减少

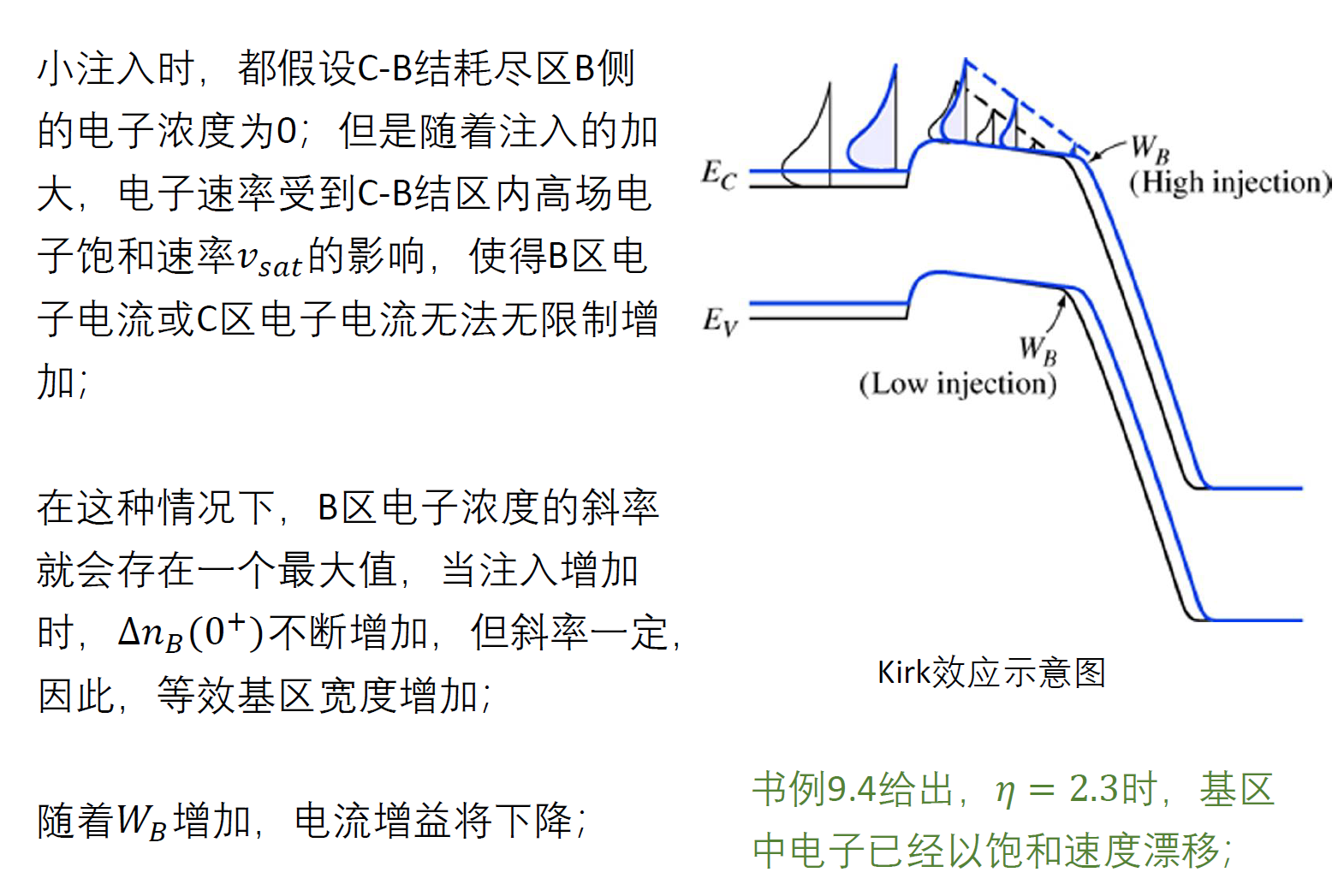

Kirk效应

收到饱和速率𝑣𝑠𝑎𝑡影响,B区电子电流或C区电子电流无法无限制增加,斜率有极大值,当浓度太高,基区会变长,β减少

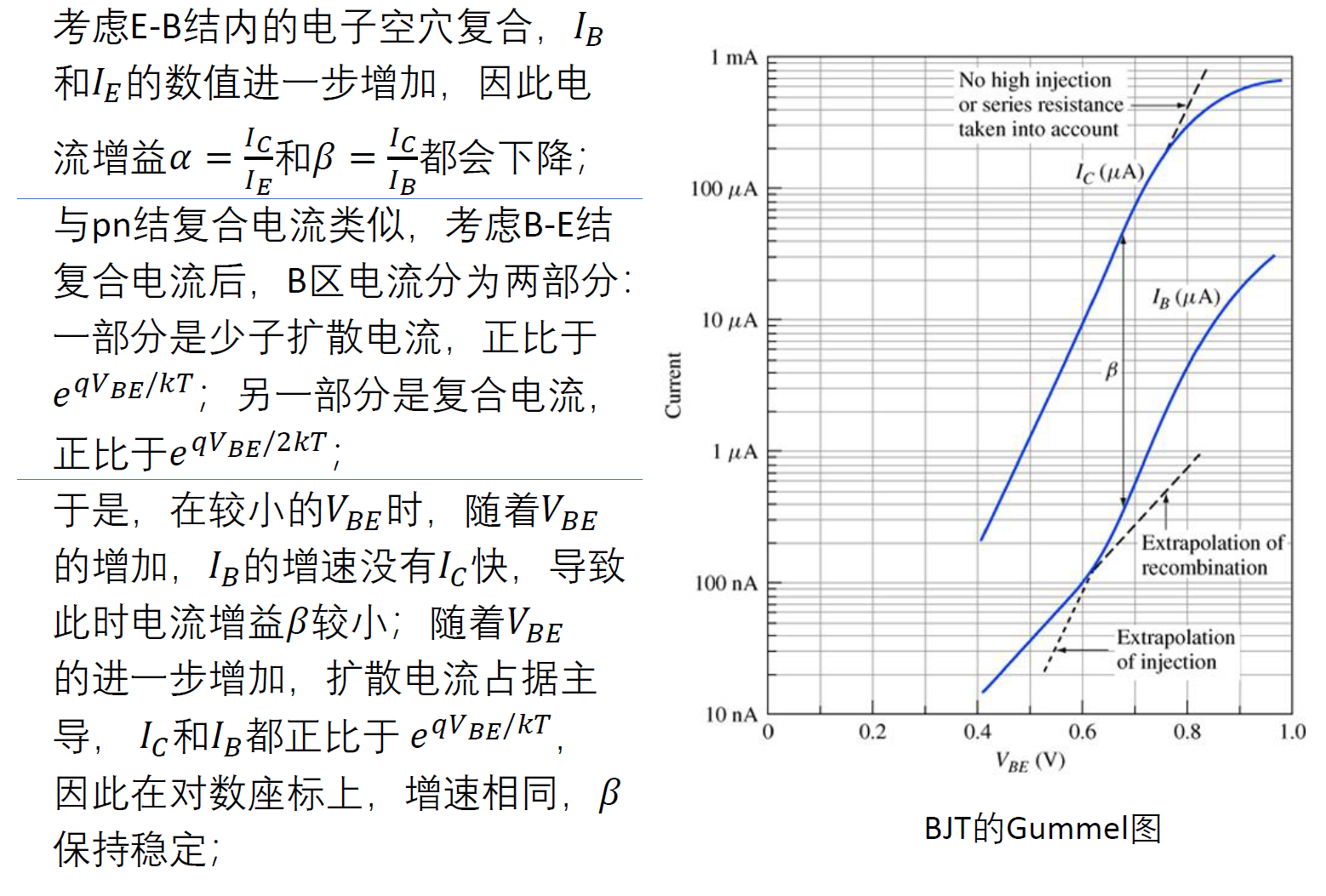

EB结内复合

小Vbe,Ib没有Ic增速快,β少

习题

3.19

3.25

3.26

9.1

9.8

9.13

9.17

10.1

10.4

11.6

11.7

11.14

11.18

公式

$$\eta={\frac{W_{B}}{\lambda,}}=\ln\frac{N_{A}(0^{+})}{N_{A}(W_{B})}$$